西藏昌都/动态光伏板组件回收

在我们刚一始接触到51单片机的时候对P0口必须加上上拉电阻,否则P0就是高阻态。对这个问题可能感到疑惑,为什么是高阻态?加上拉电阻?今天针对这一概念进行简单讲解。高阻态高阻态这是一个数字电路里常见的术语,指的是电路的一种输出状态,既不是高电平也不是低电平。如果高阻态再输入下 电路的话,对下级电路无任何影响,和没接一样,如果用万用表测的话有可能是高电平也有可能是低电平,随它后面接的东西定。高阻态的实质电路分析时高阻态可路理解,你可以把它看作输出(输入)电阻非常大。

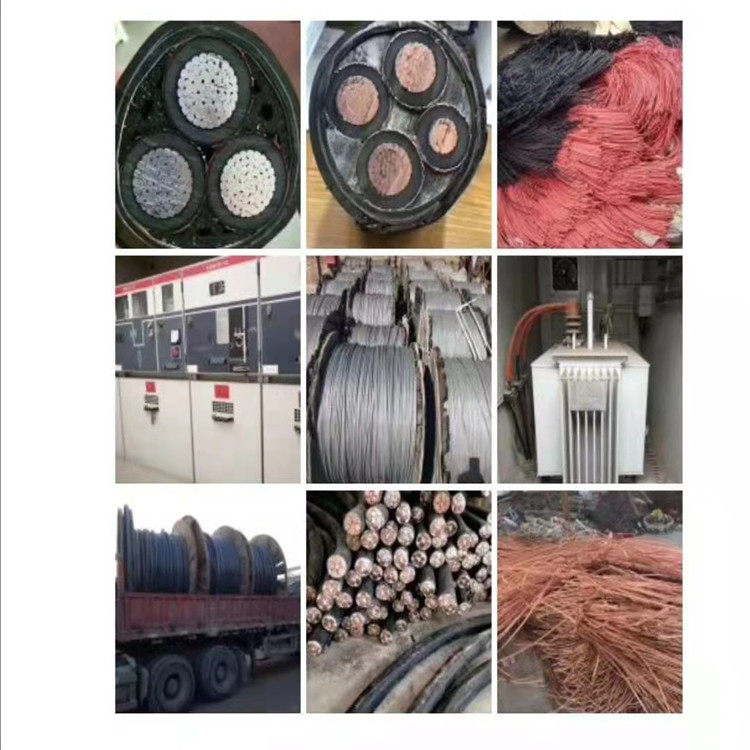

废旧电缆利用方法

1.手工剥皮法:该法采用人工进行剥皮,效率低、成本高,而且工人的操作环境较差;

2.焚烧法:焚烧法是一种传统的方法,使废线缆的塑料皮燃烧,然后其中的铜,但产生的烟气污染极为严重,同时 ,在焚烧过程中铜线的表面严重氧化,降低了金属率,该法已经被各国严格禁止;

3.机械剥皮法:采用线缆剥皮机进行,该法仍需要人工操作,属半机械化,劳动强度大,效率低,而且只适用粗径线缆;

4.化学法:化学法废线缆技术是在上个世纪90年代提出的,一些 曾进行研究,我国在“八五”期间也进行过研究。该法有一个的缺点是产生的废液无法,对环境有较大的影响,故很少采用;

5.冷冻法:该法也是上个世纪九十年代提出的,采用液氮制冷剂,使废线缆在极低的温度下变脆,然后经过破碎和震动,使塑料皮与铜线段分离,我国在“八五”期间也曾经立项研究,但此法的缺点是成本高,难以进行工业化的生产

西藏昌都( /动态)光伏板组件

质量和信誉是我们存在的基石。我们注重客户提出的每个要求,充分考虑每一个细节,积极的好服务,电缆电线、外力损伤。由近几年的运行分析来看,尤其是在经济高速发展中的海浦东,现相当多的电缆故障都是由于机械损伤引起的。比如:电缆敷设时不规范施工,容易造成机械损伤;在直埋电缆上搞土建施工也极易将运行中的电缆损伤等。有时如果损伤不严重,要几个月甚至几年才会导致损伤部位击穿形成故障,有时破坏严重的可能发生短路故障,直接影响电『舣J和用电单位的安全生产。绝缘受潮。这种情况也很常见,一般发生在直埋或排管里的电缆接头处。比如:电缆接头不合格和在潮湿的气候条件下接头,会使接头进水或混入水蒸气,时间久而在电场作用下形成水树枝。

在变频控制中,目前常用的是三相逆变桥,就像下面的图中一样。三相逆变桥中的U1,U2,V1,V2,W1,W2是控制6个IGBT的驱动信号;而三相逆变桥U,V,W分别接电机的三相绕组的引出端;三相逆变桥的工作原理这里简单介绍一下,逆变桥的上端接的是直流电压的正端,下端接的是直流电压的负端,这里该直流电压为VDC。三相桥由三个桥臂组成,如上图中U1,U2控制的IGBT组成一个桥臂;V1,V2控制的IGBT组成第二个桥臂;W1,VW2控制的IGBT组成第三个桥臂;所以当U1是高电平,且U2是低电平时,上臂的IGBT通,下臂的IGBT关断,这样的话电机的U相对逆变桥的负端电压就约为该逆变桥的直流电压值,即为VDC。交流接触器分为两部分:线圈和衔铁,它主要有三组主触点,另外搭配一组或者两组多组辅助触点,辅助触点又分为常和常闭。当线圈通电的时候,线圈产生磁场,通过铁芯把衔铁吸下来。而衔铁又带动所有的触点动作,主触点闭合,常触点闭合,常闭触点断。主触点允许通过的电流较大,一般用来控制主线路的通断。辅助触点一般用于小电流的控制电路。带一组常闭辅助触点的接触器CJX20901的含义:C表示接触器,J表示交流,X表示小型,2表示设计序号,09表示额定工作电流是9A,01表示有0组常辅助触点1组常闭辅助触点。一般的显示器3000元就能搞定,而几十寸的大屏幕显示器,根据品牌不同可能价格相差几千元。线路的选择,也是影响价格的因素。可以采取直接布线,也可以使用无线路由。当然无线的更贵,而且传输的信号容易受到物理因素的影响,使用直接布线的方法。根据实际取用情况,决定线缆长度。品牌和质 定。 ,看是自己还是需要请工人来,这又是一笔费用,一般费需要200-350左右一个点位。热继电器的形式多样,常用的有双金属片式和热敏电阻式,目前使用 多的是双金属片式,同时有的规格还带有断相保护功能。双金属片热继电器主要由主双金属片、热元件、复位按钮、动作机构、触点系统、电路调节旋钮、复位机构和温度补偿元件等构成。当电动机正常运行时,热元件产生的热虽然能使主双金属片弯曲,但是弯曲产生的推动力不足以使热继电器的触点动作。当电动机过载时,双金属片的弯曲位移加大,推动导板使常闭触点断,通过控制电路使得交流接触器断电分闸从而切断电动机的工作电源,由此保护了电动机。场效应管通常分为两类:JFET和MOSFET。这两类场效应管都是压控型的器件。场效应管有三个电极,分别为:栅极漏极D和源极S。目前MOSFET应用广泛,JFET相对较少。MOSFET可以分为NMOS和PMOS,下图是PMOS的结构图、NMOS和MOSFET的电路符号图。PMOS的结构是这样的:在N型硅衬底上了两个P型半导体的P+区,这两个区分别叫源极S和漏极D,在N型半导体的绝缘层上引出栅极G。